SmartNIC và DPU là giải pháp mạng thế hệ mới dành cho các hệ thống có lưu lượng mạng cao. Để xác định xem SmartNIC hay DPU phù hợp hơn với hệ thống của mình, các quản trị viên cần hiểu khả năng của các loại NIC và DPU khác nhau.

Môi trường CNTT truyền thống không còn thích hợp cho nhiều tổ chức, đặc biệt là những tổ chức xử lý lượng lớn dữ liệu. SmartNIC phù hợp với một số công ty nhất định, nhưng còn những công ty khác có thể sẽ cần DPU ở cấp độ hyperscale.

NIC (Network Interface Card) đã phát triển theo thời gian để đáp ứng nhu cầu chu chuyển dữ liệu mạng ngày càng tăng và hiện nay cơ bản đã có một số loại khác nhau. Các NIC cơ bản và nền tảng là thứ mà hầu hết các quản trị viên mạng và máy chủ đều quen thuộc. Nó thường đi kèm sẵn với các máy chủ, hỗ trợ các mức tốc độ 1Gbps, 10Gbps, 25Gbps và thậm chí lên đến 50Gbps. Đối với hầu hết các ứng dụng tiêu chuẩn – có ảo hóa hoặc không – các NIC này đều ổn. Chúng ít tốn kém chi phí nhất và thường là quá đủ để đáp ứng các nhu cầu thông dụng. Chúng còn được gọi là các “dump NIC”, vì chúng giao quá trình xử lý gói tin mạng cho CPU máy chủ. Tuy nhiên, khi tốc độ mạng tăng lên, gánh nặng xử lý gói tin mạng trên CPU máy chủ cũng tăng theo.

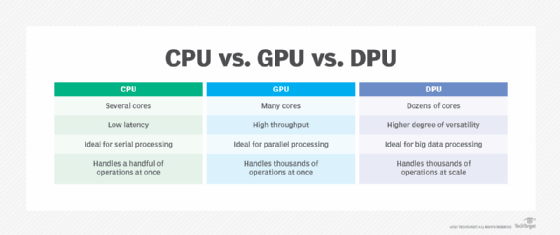

Sự phổ biến ngày càng nhiều của các dãy tốc độ thậm chí còn cao hơn – chẳng hạn như mạng 100Gbps, 200Gbps và cả 400Gbps! – đã làm thay đổi hệ sinh thái, đặc biệt là đối với mạng dành cho hệ thống lưu trữ. Những mức tốc độ cao hơn nhiều này đã đẩy tải xử lý của CPU lên rất cao, thường vượt quá 30% trên các CPU máy chủ. Các chu kỳ CPU máy chủ để xử lý gói tin mạng không còn có thể được sử dụng để xử lý cho ứng dụng. Chính điều này dẫn đến sự ra đời của các NIC có nhiệm vụ giảm tải (offload NIC) cho CPU.

“Offload NIC” là cứu cánh

Các offload NIC đã được đưa ra thị trường vài lần trong quá khứ, nhưng ở thời điểm hiện nay thì có sự khác biệt rõ rệt. Trong lịch sử, khi các CPU có các transistor tuân theo định luật Moore, các NIC giảm tải trở thành một lựa chọn đắt tiền và không cần thiết. Tuy nhiên, định luật Moore đã chậm lại trong vài năm qua. Sự chậm lại đó đã làm cho các NIC giảm tải trở nên khả thi. Chúng có khuynh hướng giảm tải các chức năng chu chuyển lưu lượng mạng, chẳng hạn như xử lý gói tin ở lớp TCP/IP. Điều này giải phóng CPU máy chủ để trả lại các chu kỳ quay trở lại với các ứng dụng.

Các NIC giảm tải rất hữu ích khi so sánh với các NIC tiêu chuẩn đã làm cho các máy chủ chạy chậm lại. Một khi NIC làm chậm máy chủ, nó làm giảm số lượng máy ảo (VM) hoặc container có thể chạy hiệu quả, nghĩa là các tổ chức cần một giải pháp giảm tải – hoặc nhiều máy chủ vật lý hơn. Thật dễ dàng để lý giải cho việc giá của offload NIC cao hơn khi chúng có thể giúp giảm số lượng máy chủ vật lý cần thiết.

SmartNIC đưa việc giảm tải lên một bước cao hơn

Nhiều tổ chức xác định rằng offload NIC là không đủ đối với họ. Dẫn đến sự ra đời của SmartNIC, không chỉ làm giảm tải ở lớp TCP/IP. Chúng linh hoạt hơn một chút so với offload NIC và chúng có một cơ chế xử lý dễ lập trình hơn. Các SmartNIC giảm tải nhiều nhu cầu xử lý mạng hơn từ CPU máy chủ. Trên thực tế, chúng có CPU, bộ nhớ và hệ điều hành riêng. Những gì chúng giảm tải khác nhau tùy theo nhà cung cấp, nhưng SmartNIC có thể giảm tải các tác vụ như nén và giải nén dữ liệu mạng, mã hóa và giải mã và thậm chí cả các tính năng bảo mật.

Các SmartNIC thường có giá cao hơn các NIC giảm tải. Tuy nhiên, khi các máy chủ bị sa lầy một lần nữa với quá trình xử lý nén và giải nén, hoặc mã hóa và giải mã, thay vì bổ sung thêm nhiều máy chủ hơn, SmartNICs trở thành một lựa chọn hiển nhiên ưu việt hơn.

Tuy nhiên, khi tốc độ mạng cao hơn đã phổ biến trên khắp các hệ sinh thái CNTT – đặc biệt là trong hệ thống mạng chuyên cho lưu trữ – các quản trị viên CNTT đang tìm kiếm thứ gì đó cần phải nhiều hơn nữa. Bước tiến tiếp theo đó là Đơn vị xử lý dữ liệu (DPU).

DPU là một bước tiến lớn của SmartNIC.

DPU là gì?

DPU là một bước tiến lớn của SmartNIC. DPU bao gồm tính năng giảm tải, pipeline linh hoạt cho việc lập trình, khả năng xử lý và CPU riêng của SmartNIC. Nhưng DPU là điểm cuối của hạ tầng mạng, chứ không phải máy chủ mà nó được lắp vào. DPU bao gồm các con chip tùy chỉnh và trong một số trường hợp, là các FPGA (field-programmable gate array) tùy biến hoặc các mạch tích hợp dành riêng cho ứng dụng tùy biến. DPU có thể hỗ trợ nhiều thứ hơn một SmartNIC, bao gồm kết nối mạng dựa trên P4 programmable pipeline, stateful Layer 4 firewall, L2/L3 networking, L4 load balancing, storage routing, storage analytics và VPN. Chức năng của DPU khác nhau tùy theo nhà cung cấp. Một số công ty lớn trên thị trường năm 2022 là NVIDIA, Fungible, AMD Pensando và Marvell.

DPU giúp hỗ trợ cho hệ thống lưu trữ hiệu suất cao. Chúng giảm các vấn đề về mạng lưu trữ được chia sẻ và cung cấp độ trễ lưu trữ tương đương với lưu trữ NVMe được nhúng trong các máy chủ. Đó là một thành tựu đáng kể, nhưng nó vẫn có thể không đủ cho mạng lưu trữ hiệu suất cao. Vấn đề lần này là mạng chuyển mạch.

Các thiết bị chuyển mạch không thể hỗ trợ quy mô lớn hoặc mức độ hyperscale, điều này đã không tồn tại cho đến khi có sự xuất hiện của các hệ thống “hyperscaler”, chẳng hạn như của Meta và các nhà cung cấp dịch vụ đám mây công cộng như AWS, Azure, Google Cloud Platform, Oracle, IBM và Alibaba. Sự thiếu sót này của các thiết bị chuyển mạch đã bắt đầu hình thành nên tình huống khó khi các tổ chức đã phát hiện ra giá trị nội tại của dữ liệu mà họ cần phải phân tích và khai thác bằng cơ sở dữ liệu phân tích, học máy và AI.

Số lượng dữ liệu đang được phân tích từ petabyte đến cấp exabyte – những khối lượng chưa từng có cách đây vài năm. Trong các quy trình phân tích dữ liệu này, độ trễ là cực kỳ quan trọng. Kiến trúc lá (leaf) của các thiết bị chuyển mạch cuối làm tăng quá nhiều độ trễ ở các cấp độ hyperscale, đặc biệt với cái gọi là ‘tail latency’. Độ trễ không thể đoán trước thậm chí còn tệ hơn. Điều này đã dẫn đến sự phát triển của các hyperscale DPU.

DPU lý tưởng cho các hệ thống mạng lưu trữ. Chúng có giá cao hơn các NIC khác, nhưng chúng làm được nhiều hơn và có thể làm cho hệ thống lưu trữ hiệu quả hơn với độ trễ thấp hơn. Điều đó có thể làm giảm số lượng bộ điều khiển lưu trữ cần thiết cho một ứng dụng hiệu suất cao nhất định.

Các Hyperscale DPU sẽ tiến thêm một bước nữa

Các Hyperscale DPU có khả năng lập trình cực kỳ cao và chúng loại bỏ việc chuyển mạch theo hướng west-east. Chúng không loại bỏ chuyển mạch north-south. Chúng thường được triển khai ở dạng một lưới hình xuyến, hoặc nhiều mô hình kết nối khác. Mellanox (thuộc NVIDIA) hiện là một trong các nhà cung cấp DPU cấp độ hyperscale.

Hyperscale DPU thực hiện mọi thứ mà DPU làm và hơn thế nữa. Chúng giảm độ trễ đầu cuối và độ trễ đó có thể dự đoán được, nhưng chúng không nhất thiết phải đắt tiền hơn DPU. Và chúng loại bỏ rất nhiều chi phí bằng cách giảm đáng kể hạ tầng chuyển mạch.

Bài viết liên quan

- NVIDIA NVLink Fusion: Tương lai của Trung tâm Dữ liệu AI

- NVIDIA ConnectX-8 SuperNIC – Nền tảng switch siêu tốc cho các máy chủ MGX có 8x GPU PCIe

- NVIDIA ConnectX-8 SuperNIC: Đột phá kiến trúc hạ tầng AI với PCIe Gen6

- Hướng dẫn cấu hình chi tiết từng lệnh cho thiết bị switch Spectrum của NVIDIA

- Tìm hiểu các công nghệ mạng của NVIDIA: Nền tảng cho HPC và AI

- AI và Network: Hai mặt của đồng xu định hình hạ tầng điện toán tương lai